The ARM architecture is the foundation for building each ARM processor. The ARM architecture evolves over time and includes architectural features to meet the growing demands of new features, high performance requirements, and emerging markets. For information on the latest published version, see the ARMv8 architecture.

The ARM architecture supports implementations that span multiple performance points and has become the dominant architecture in many market segments. The ARM architecture supports a wide range of performance points, enabling the use of the latest microarchitectural technology to achieve very small ARM processor implementations and extremely efficient advanced design implementations. Achieving scale, performance, and low power is a key feature of the ARM architecture.

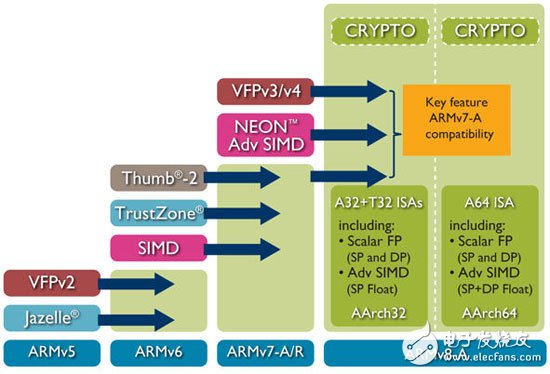

ARM has developed architectural extensions to support Java Acceleration (Jazelle®), Security (TrustZone®), SIMD, and Advanced SIMD (NEONTM) technologies. The ARMv8-A architecture adds password extension as an optional feature.

The ARM architecture is similar to the Reduced Instruction Set Computing (RISC) architecture because it contains the following typical RISC architectural features:

Uniform register file load/store architecture where data processing operations are only for register contents and are not directly directed to memory contents.

In simple addressing mode, all load/store addresses are determined only by register contents and instruction fields.

Enhancements to the basic RISC architecture enable ARM processors to achieve a high balance of higher performance, smaller code size, lower power consumption, and smaller silicon area.

A32 (ARM) architecture / features

ARM (commonly known as A32) is a fixed-length (32-bit) instruction set. It is the underlying 32-bit ISA used in the ARMv4T, ARMv5TEJ, and ARMv6 architectures. In these architectures, the instruction set is used in applications that require high performance, or to handle hardware exceptions such as interrupts and processor startup.

For performance-critical applications and legacy code, the CortexTM-A and Cortex-R profiles for the Cortex architecture also support ARM ISA. Most of its features are included in the Thumb instruction set introduced with Thumb-2 technology. Thumb (T32) benefits from improved code density.

The ARM instruction is 32 bits long and requires a 4-byte boundary alignment.

Most ARM instructions can be "conditionalized" so that they are only executed when a previous condition has a specific condition code set. This means that if the N, Z, C, and V flags in the application status register satisfy the conditions specified in the instruction, the instruction only plays its normal role for the programmer's model operations, memory, and coprocessor. If these flags do not satisfy this condition, the instruction will be used as a NOP, that is, the execution process will normally enter the next instruction (including any related checks on the exception), but will not play any other role. This conditional instruction allows a small portion of the if and while statements to be encoded without the use of a jump instruction.

Condition code N: Negative condition code, set to 1 if the result is negative

Condition code Z: Zero condition code, set to 1 if the result of the instruction is 0

Condition code C: Carry condition code, set to 1 if the instruction generates a carry condition

Condition code V: Overflow condition code, set to 1 if the instruction generates an overflow condition.

T32 (Thumb) architecture / features

Cost-sensitive embedded control applications such as cell phones, disk drives, modems, and pagers have been seeking to implement 32-bit performance and address space at the lowest cost in some ways while taking into account memory footprint.

The Thumb (T32) instruction set provides a subset of the most commonly used 32-bit ARM instructions that have been compressed to a 16-bit wide opcode. When executed, these 16-bit instructions are decompressed in real time and transparently into full 32-bit ARM instructions with no performance penalty.

Thumb provides designers with:

Excellent code density for minimal system memory size and lowest cost.

Reduces system cost by enabling 32-bit performance in 8-bit or 16-bit memory on 8-bit or 16-bit buses.

Established ARM features

Industry-leading MIPS/Watt to maximize battery life and increase RISC performance

Small chip area for integration and minimizing chip cost

A global multi-partner source provides security assurance.

Designers can use both 16-bit Thumb and 32-bit ARM instruction sets, giving them the flexibility to scale performance or resize code at the subroutine level based on application requirements.

Thumb ISA is widely supported by the ARM ecosystem, including a comprehensive Windows software development environment and development and evaluation cards.

Improved code density for performance efficiency and efficiency

Thumb-2 technology makes Thumb a mixed (32-bit and 16-bit) length instruction set that is common to all ARMv7-compatible ARM Cortex implementations. Thumb-2 improves the performance, energy efficiency, and code density of many embedded applications.

This technology is backward compatible with existing ARM and Thumb solutions, while significantly extending the available features of the Thumb instruction set, enabling more applications to benefit from Thumb's best-in-class code density. For performance-optimized code, Thumb-2 technology uses less than 31% of memory to reduce system cost while providing 38% better performance than existing high-density code, so it can be used to extend battery life or enrich product features set.

We are saleing Touch screen for AMT,provides the product information.

Touch screen for AMT are widely used for medical and industrial equipment, research shows, machinery equipment, industrial control, man-machine interface, industrial automation integrated workstation, POS, CNC etc. we have a lot of Touch screen for AMT, standing some of our inventory stock.

Touch Screen For Amt,Touch Screen For Amt Replacement,Touch Panel For Amt

GUANGZHOU VICPAS TOUCH TECHNOLOGY CO.,LTD , https://www.touchsuppliers.com